# RAL ASIC Design Group Recent R&D experience

Mark Prydderch – ASIC Design Group Leader

mark.prydderch@stfc.ac.uk

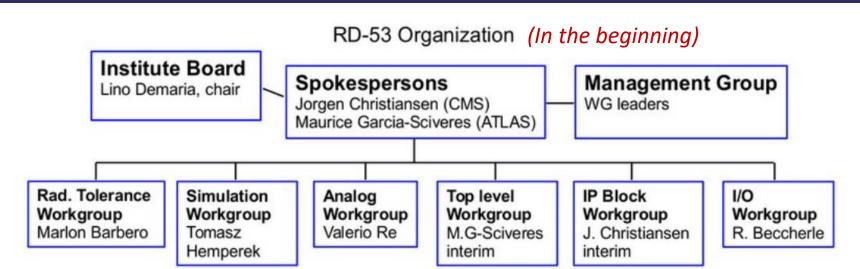

### **RD53 Collaboration**

- Collaboration structure Clear decision making processes

- Collaboration membership rules

- Collaboration agreement/MoU including IP sharing

- Funding Needs to be secure for duration of participation

We were reliant on internal funding

- Meetings & workshops, Email groups, Web site...

- Documentation Publications, author list, approvals

- Secure shared database for designs (CLIOSOFT)

Cadence Design Share Agreement might now be

Science at a barrier to doing this, or at least a hindrance

Technology

Facilities Council

The extent to which CERN's proposed

28nm NDA is available to institutes might also be an issue in future...

DESIGN SHARE AGREEMENT

RELATED TO THE

EUROPRACTICE SOFTWARE SERVICES

ACADEMIC AND RESEARCH LARDEATORY END USER AGREEMENT

AGREEMENT DATE:

END USER: END USER ADDRESS

END USER AGREEMENT EFFECTIVE DATE:

RECIPIENT NAME:

RECIPIENT ADDRESS:

This Design Stare Agreement ("Agreement") is under among the End User and Racipient identified above and, Cadence Design Systems Limited ("Cadence"), with an office located at Maria 1, Western Road, Brackeall, RO12 IRT, United Kinzelson. Capitalized words not defined in this Agreement shall have the meaning eastered in the RUNGERACITICS. Software Services Academic and Research Laboratory End User Agreement identified above ("Bad User Agreement").

#### Background

A. In the End User Agreement, End User agreed that use of the Cadence Products is restricted solely to a non-commercial, nonproduction (a) educational use and (b) Fundamental Research.

Connection), Revised 31 Int 2020 Calence

Collaboration meeting RAL 2014

**RD Collaboration Proposal:**

Development of pixel readout integrated circuits for extreme rate and radiation

ABSTRACT: The present hybri ment. They deployed a new tablished pixel tracking as ind hybrid pixel technology to the new RD collaboration specific (IC). The IC challenges inclu rates (1-2 GHz/cm²), unpreced and large IC format with low I the material budget low.

We propose a collaboration to the ATLAS and CMS Phase use the same exact pixel rean needed is independent of the are possible using the same to be effective, this collabora and not on more general chip The collaboration will have an around work groups. The fol ATLAS: Bonn, CPPM, LBNL Bari, Bergamo-Pavia, Fermill (also on CLIC) and RAL.

Memorandum of Understanding<sup>1</sup>

for the

**RD53** Collaboration

between

The EUROPEAN ORGANIZATION FOR NUCLEAR RESEARCH, "CERN", an Intergovernmental Organization having its seat at Geneva, Switzerland as Host Debarators.

on the one hand

and

The Collaborating Institutes/Funding Agencies of the RD53 Collaboration on the other hand

#### WHEREAS

- A group of Institutes from CERN Member and non-Member States, and CERN, have agreed to collaborate to from the RD53 Collaboration. This Collaboration has proposed to Institutes and CERN a Research and Development (RD) program for the development of pixel readout integrated circuits for extreme rate and radiation.

- The Institutes participating in the RD53 Collaboration pursue a coordinated effort of research and development described in the proposal described in the Letter of Intent CERN-LHCC-2013-008 (LHCC-P-006). The proposal way presented to LHC Committee on June 12<sup>th</sup> 2013 and received

- the recommendation to create a RD group.

The CERN Research Board approved the RD53 Collaboration at its 205th meeting on August 28th 2013.

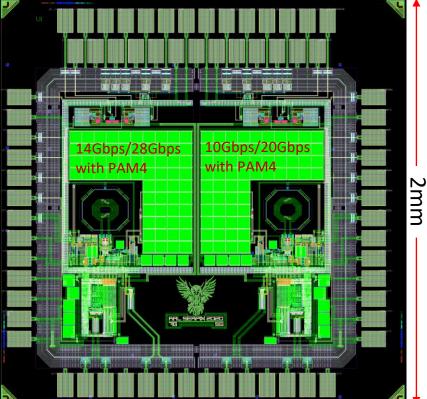

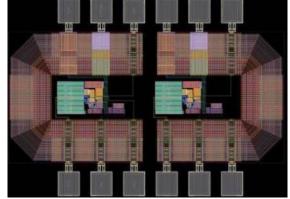

## **Internal IP development programme**

- Limited funding subject to approval & yearly finances

- Developing experience with new technologies

- ❖ IP not exclusive to Particle Physics applications

- ❖ Starting to explore 28nm with further IP development planned

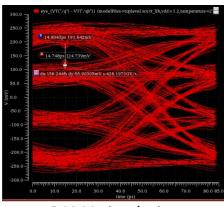

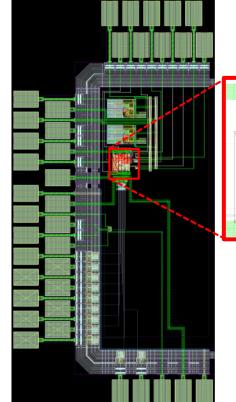

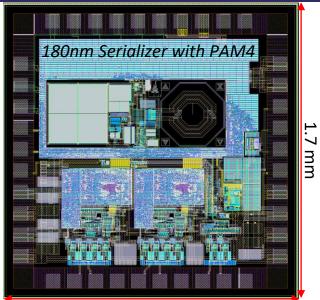

65nm Serializers with PAM4 option

2mm

350.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

300.0

NRZ simulation

PAM4 simulation

Rail-to-rail Voltage Driver for RD53

Direct-to-Digital Test Structure

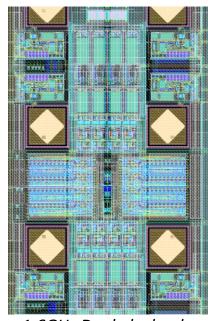

1.7 mm

HDR pixel

1.6GHz Dual-clock-edge 12-bit TDC

## Thank you

**Facebook:** Science and Technology Facilities Council

Twitter: @STFC\_matters

YouTube: Science and

**Technology Facilities Council**