### About me

#### Kristian Harder

PhD Hamburg University/DESY 1998–2002:

QCD analysis (OPAL, TESLA)

track reconstruction software (TESLA)

#### Fermilab 2002-2006:

electroweak analysis (DØ) silicon detector back-end electronics (DØ)

#### **RAL 2006-:**

silicon detector simulation (ILC)

exotica analysis (CMS)

readout+trigger electronics (CMS, DUNE)

### **About this lecture**

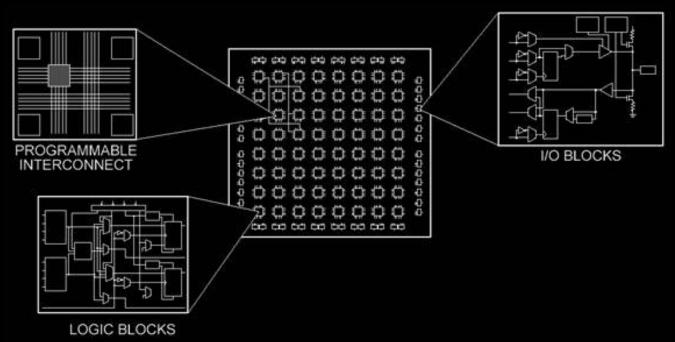

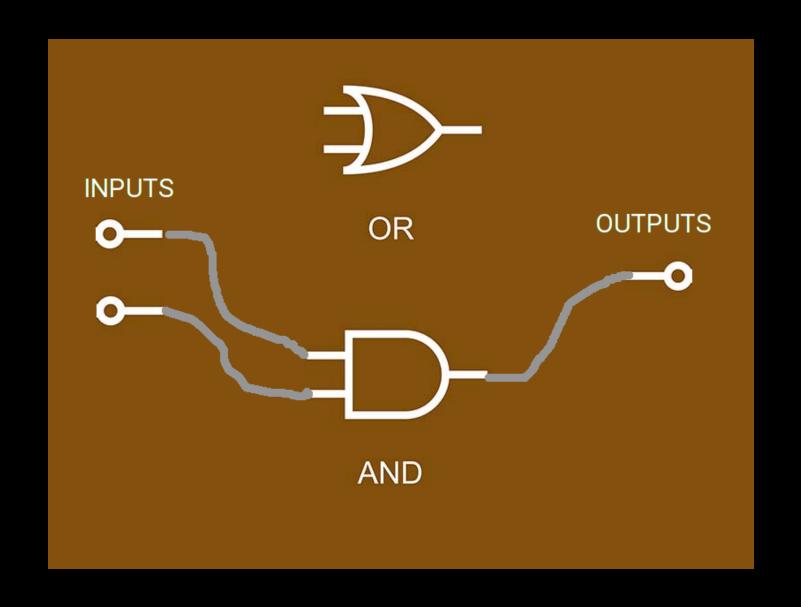

#### Field Programmable Gate Array

an integrated circuit consisting of

- \* a large number of blocks with logic gates

- tonnected by a programmable interconnection fabric

- \* accessible through I/O blocks

Program your own electronic circuit onto this chip, anywhere, anytime! (within available resources)

### lookup tables

A look-up table is a small memory bank that encodes a general logic function:

| input A | input B | input C | output |

|---------|---------|---------|--------|

| 0       | 0       | 0       | 0      |

| 0       | 0       | 1       | 1      |

| 0       | 1       | 0       | 1      |

| 0       | 1       | 1       | 0      |

| 1       | 0       | 0       | 1      |

| 1       | 0       | 1       | 0      |

| 1       | 1       | 0       | 0      |

| 1       | 1       | 1       | 1      |

LUTs can be programmed to act as basic logic gates (AND, OR, etc),

but also as complex combinations.

# modern logic blocks

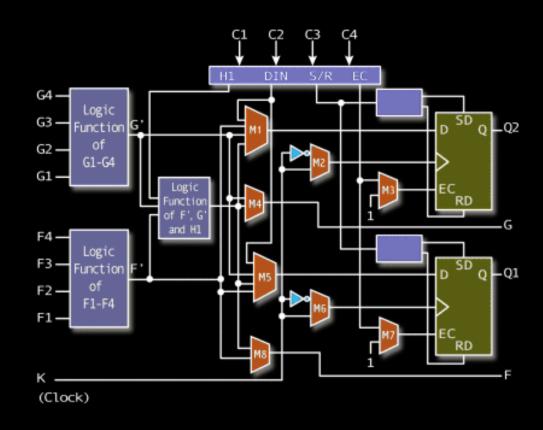

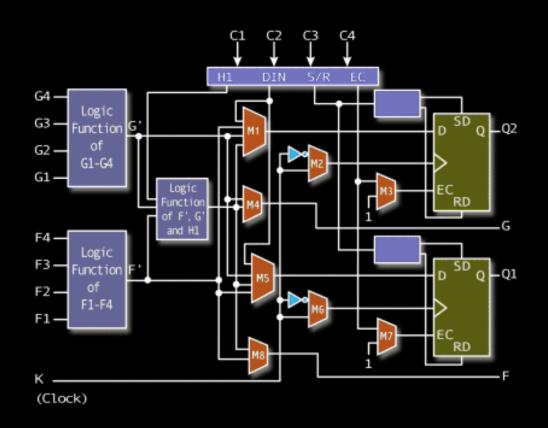

#### Configurable logic block by Xilinx (probably outdated):

- look-up tables to manipulate inputs

- multiplexers to route the signals

- \* flip-flops (clocked storage devices) to hold the outputs

- multiple blocks running on same clock for synchronous operation

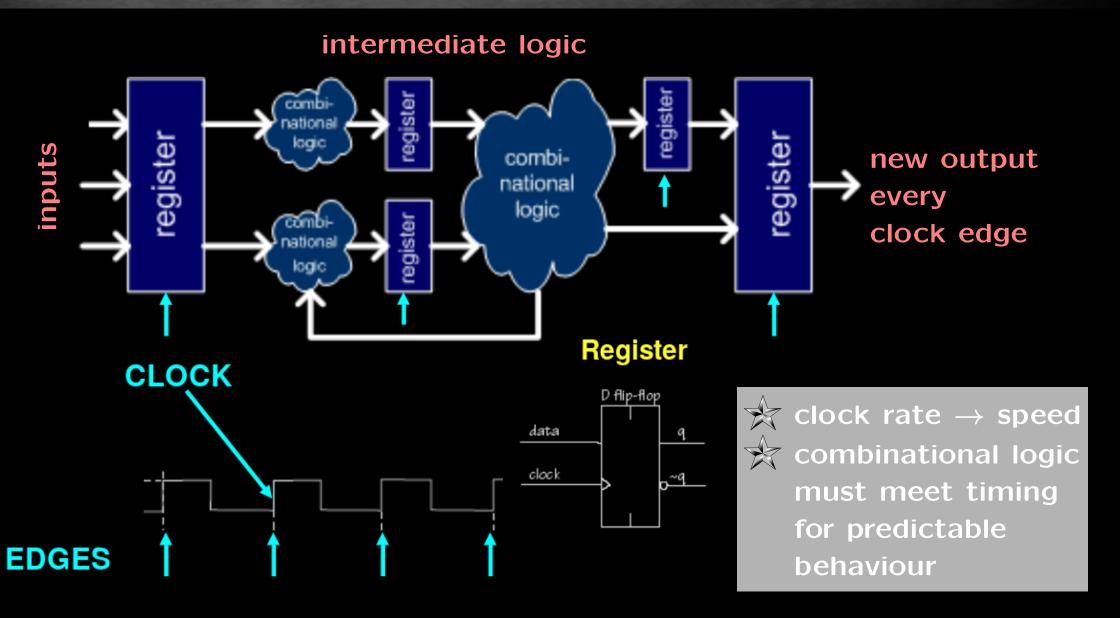

# synchronous sequential logic

graph by Edward Freeman (STFC)

### modern logic blocks

#### Configurable logic block by Xilinx (probably outdated):

#### other blocks on modern FPGAs:

high speed transceivers, PCIe interfaces, ethernet interfaces, memory banks, clock generators, DSPs, interfaces for external RAM, even entire CPUs... (but typically digital electronics only)

#### modern FPGAs

# example of resources available on current generation FPGAs: Xilinx Virtex Ultrascale+ devices

| Device Name                                 | VU3P  | VU5P  | VU7P  | VU9P  | VU11P | VU13P  | VU19P |

|---------------------------------------------|-------|-------|-------|-------|-------|--------|-------|

| System Logic Cells (K)                      | 862   | 1,314 | 1,724 | 2,586 | 2,835 | 3,780  | 8,938 |

| CLB Flip-Flops (K)                          | 788   | 1,201 | 1,576 | 2,364 | 2,592 | 3,456  | 8,172 |

| CLB LUTs (K)                                | 394   | 601   | 788   | 1,182 | 1,296 | 1,728  | 4,086 |

| Max. Dist. RAM (Mb)                         | 12.0  | 18.3  | 24.1  | 36.1  | 36.2  | 48.3   | 58.4  |

| Total Block RAM (Mb)                        | 25.3  | 36.0  | 50.6  | 75.9  | 70.9  | 94.5   | 75.9  |

| UltraRAM (Mb)                               | 90.0  | 132.2 | 180.0 | 270.0 | 270.0 | 360.0  | 90.0  |

| HBM DRAM (GB)                               | -     | -     | -     | -     | -     | -      | -     |

| HBM AXI Interfaces                          | -     | -     | -     | -     | -     | -      | -     |

| Clock Mgmt Tiles (CMTs)                     | 10    | 20    | 20    | 30    | 12    | 16     | 40    |

| DSP Slices                                  | 2,280 | 3,474 | 4,560 | 6,840 | 9,216 | 12,288 | 3,840 |

| Peak INT8 DSP (TOP/s)                       | 7.1   | 10.8  | 14.2  | 21.3  | 28.7  | 38.3   | 10.4  |

| PCle* Gen3 x16                              | 2     | 4     | 4     | 6     | 3     | 4      | 0     |

| PCIe Gen3 x16/Gen4 x8 / CCIX <sup>(1)</sup> | -     | -     | -     | -     | -     | -      | 8     |

| 150G Interlaken                             | 3     | 4     | 6     | 9     | 6     | 8      | 0     |

| 100G Ethernet w/ KR4 RS-FEC                 | 3     | 4     | 6     | 9     | 9     | 12     | 0     |

| Max. Single-Ended HP I/Os                   | 520   | 832   | 832   | 832   | 624   | 832    | 1,976 |

| Max. Single-Ended HD I/Os                   |       |       |       |       |       |        | 96    |

| GTY 32.75Gb/s Transceivers                  | 40    | 80    | 80    | 120   | 96    | 128    | 80    |

NB: very difficult to use anywhere near 100% of those resources due to limitations of the interconnection fabric

CPUs and FPGAs are capable of performing arbitrary tasks depending on programming.

But the approach is fundamentally different:

#### **CPU**

rigid silicon — the processing units remain fixed (except basics like enabling/disabling cores in multicore processors) Flexibility from stepping through instructions provided in memory

#### **FPGA**

flexibility arises from reconfiguring the fabric itself, producing a highly specialised processing unit

- very different type of device

- major differences in how they are being programmed

- x suitable for different types of application

example: edge detection in histogram (e.g. line of video pixels)

#### **CPU**

scan a line like

```

for i in range(1,17):

edge[i] = (abs(hist[i]-hist[i-1])>thres)

```

example: edge detection in histogram (e.g. line of video pixels)

#### **CPU**

scan a line like

```

for i in range(1,17):

edge[i] = (abs(hist[i]-hist[i-1])>thres)

```

#### **FPGA**

instantiate a bunch of comparators, get result in O(1) clock cycle

example: edge detection in histogram (e.g. line of video pixels)

#### **CPU**

scan a line like

```

for i in range(1,17):

edge[i] = (abs(hist[i]-hist[i-1])>thres)

```

#### **FPGA**

instantiate a bunch of comparators, get result in O(1) clock cycle

FPGA benefits from parallel instantiation of a large number of specialised logic circuits

NB: GPUs are somewhat in the middle — massive parallelisation with simplified CPUs

### **FPGA** applications

FPGAs offer advantages over CPUs for specific applications:

- \* high degree of parallelisation, pipelining

- many high speed data links

- $\bigstar$  precise control over data path o fixed latency

- > low latency (if done right)

**FPGAs** have weaknesses too:

- complex arithmetic (floating point numbers etc)

- cost (depending on parameters)

### **FPGA** applications

#### Use of FPGAs in particle physics

- \* L1 trigger

- **★** DAQ

- clock distribution (incl fast commands, triggers)

#### FPGA use elsewhere

- high performance computing: FPGAs supporting CPUs

- aerospace, automotive, telecommunications, BitCoin mining

- prototyping of new ASICs

### **FPGA** applications

#### Use of FPGAs in particle physics

- ★ L1 trigger

- **★** DAQ

- clock distribution (incl fast commands, triggers)

#### FPGA use elsewhere

- high performance computing: FPGAs supporting CPUs

- aerospace, automotive, telecommunications, BitCoin mining

- prototyping of new ASICs

Note on ASICs (Application Specific Integrated Circuits): actual custom chips can have higher speed, higher density, lower power, more resources, can be cheaper in large quantities, require no in situ programming

BUT: much longer time to availability, mistakes are expensive

we typically use them only in detector front-end

### **FPGA** vendors

formerly Altera, about 35% market share

low power, low cost devices

low power FPGA/ASIC hybrids

low power, radiation hard, non-volatile (flash based)

...and probably others!

This lecture focusing on Xilinx — used by CMS-UK, ATLAS-UK

# commercial FPGA platforms

#### examples for commercially available FPGA boards:

FPGA accelerator card based on Altera device

FPGA RF/optical I/O card based on Xilinx device

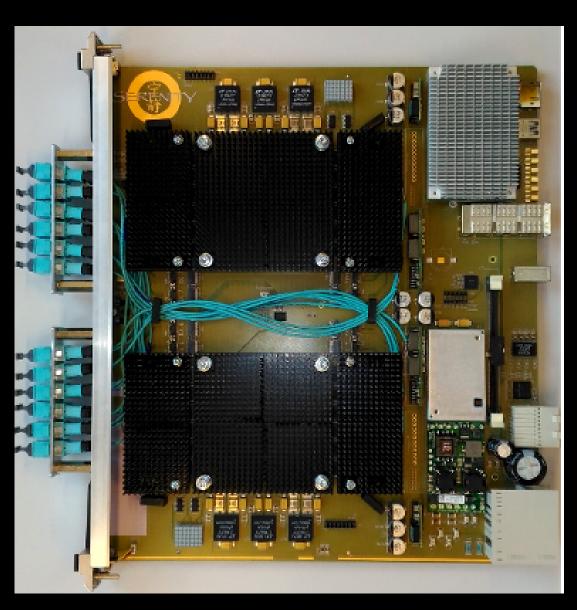

### custom hardware

#### Imperial College's Serenity board

- multi-purpose board

- mostly for CMS upgrade

- two FPGA sites

- FPGAs easily replaceable

- optical high speed links

- \* ATCA form factor

- comes with single board PC

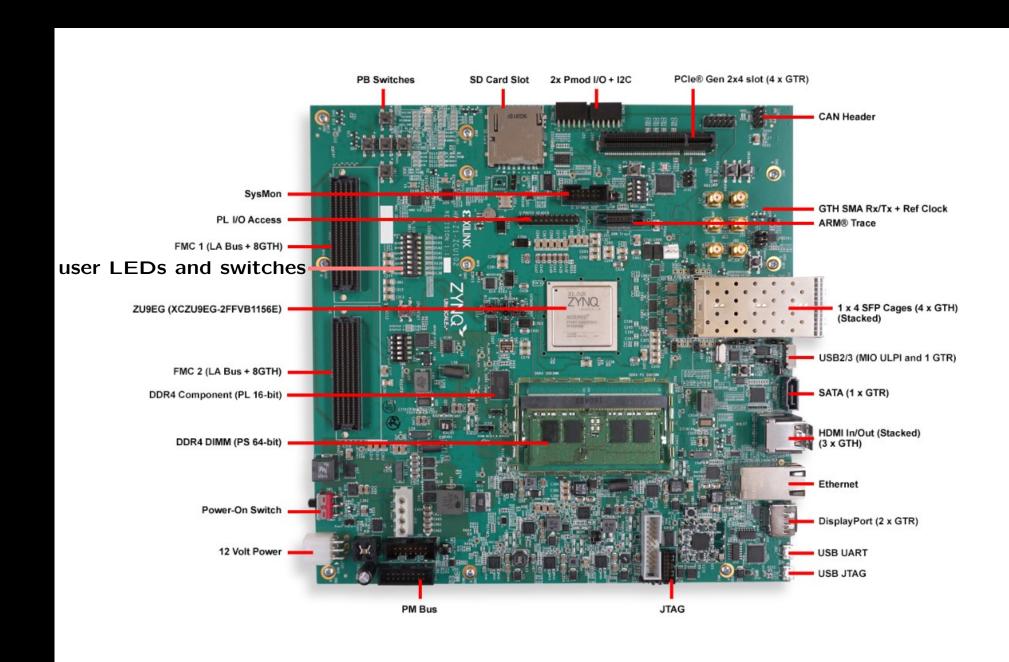

### development boards

FPGA manufacturers provide development platforms for their FPGAs: FPGA on circuit board with peripherals and infrastructure

#### benefits:

often available very early on after release of new devices

\* often relatively low cost because subsidised

#### In widespread use in our labs!

tested algorithms for Serenity long before prototypes available

\* experience can actually influence custom board design

ideal for learning: availability, example designs

### Xilinx zcu102

### How to program an FPGA

The set of configuration instructions for an FPGA

🖈 is not actually modifying hardware,

🌟 but it is not a software algorithm either.

It is somewhat in between, which is why it is called

Description either graphically as schematics, or in a hardware description language.

hardware description language looks similar to software, but is very different.

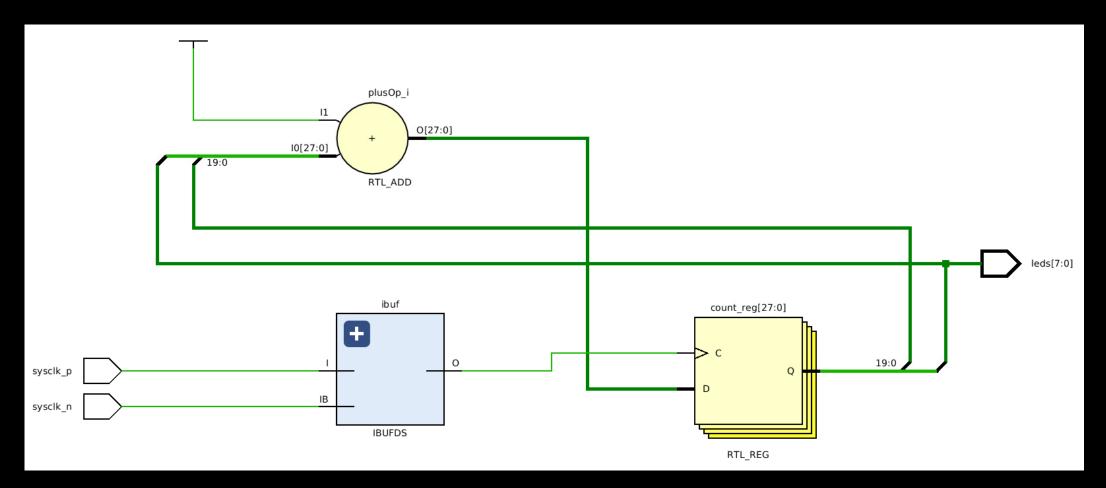

### schematics

We won't use schematics today, but we will implement <u>this</u> design. Note inputs, outputs, blocks, signals, busses, constants, and a loop! Relatively easy to understand, but not very practical for complex tasks.

### hardware description languages

#### Two main languages in use:

|                      | VHDL       | Verilog   |

|----------------------|------------|-----------|

| resemblance          | Pascal/Ada | С         |

| strong types         | yes        | no        |

| composite data types | yes        | no        |

| case sensitive       | no         | yes       |

| library management   | yes        | no        |

| who in CMS likes it  | Brits      | Americans |

```

Verilog:

VHDL:

process ({S0,S1},A,B,C,D)

begin

always @({S0,S1}, A, B, C, D)

case (S0, S1), is

case ({S0,S1})

when "00" => Y <= A;

2'b00: Y = A;

when "01" => Y <= B;

2'b01: Y = B;

when "10" => Y <= C;

when "11" => Y <= D;

2'b10: Y = C;

2'b11: Y = D;

9

when others => Y <= A;

9

10

endcase

end case;

end process;

```

from blog.digilentinc.com

# hardware description languages

#### Two main languages in use:

|                      | VHDL       | Verilog   |

|----------------------|------------|-----------|

| resemblance          | Pascal/Ada | С         |

| strong types         | yes        | no        |

| composite data types | yes        | no        |

| case sensitive       | no         | yes       |

| library management   | yes        | no        |

| who in CMS likes it  | Brits      | Americans |

We use VHDL in our projects because

tomplex data types make interfaces easier to read (and write)

\* strong typing reduces margin for error

it does seem to be a bit easier to read

Firmware design is intrinsically modular.

Can mix Verilog, VHDL and schematic design in one project.

(Prefer not to.)

### example project

Let's make some LEDs blink on our zcu102 development board! We will need:

#### **LEDs**

\* zcu102 has a block of 8 user LEDs connected to FPGA I/O pins

pin location and required voltage levels are documented

#### clock

all development boards have oscillators

some connected to FPGA directly

\* some connected through programmable clock chips

\* high speed clock signals are often differential

#### firmware

X VHDL design discussed on following pages

```

--- simple "hello world" example

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

library unisim;

8

use unisim. VComponents.all;

9

10

11 @ entity top is port(

12

sysclk p : in std logic;

13

sysclk n : in std logic;

14

: out std_logic_vector(7 downto 0)

15

16 end top;

17

18 ─ architecture rtl of top is

19

20

signal clk : std logic;

21

signal count : unsigned(27 downto 0) := (others => '0');

22

23

begin

24

25 ⊝

ibuf: IBUFDS

26

port map(

27

i => sysclk p,

28

ib => sysclk n,

29

o => clk

30 (

):

31

32 ;

33 ⊡

process(clk)

34 :

begin

35 🖯

if rising edge(clk) then

36

count <= count + 1;

37 🖨

38 🖯

end process;

39 :

40

41

leds(7 downto 0) <= std logic vector(count(27 downto 20));</pre>

42

43

44 end rtl;

```

#### This is all the VHDL we need today!

- This block connects to a differential 125 MHz clock input,

- converts the clock signal to a single-ended one,

- runs a 28 bit counter on that clock (highest bit should then alternate at about 1 Hz),

- and connects the highest (i.e. slowest) bits to LEDs

- Let's look at the code in detail

```

--- simple "hello world" example

2

3

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

6

7

library unisim;

use unisim. VComponents.all;

8

9

10

11 🖯

entity top is port(

sysclk p : in std logic;

12

sysclk n : in std logic;

13

: out std logic vector(7 downto 0)

14

15

);

16 🖨

end top;

17

18 ☐ architecture rtl of top is

19

20

signal clk : std logic;

21

signal count : unsigned(27 downto 0) := (others => '0');

22

23

begin

24

25 🖯

ibuf: IBUFDS

26

port map(

27

i => sysclk p,

28

ib => sysclk n,

29

o => clk

30 🖨

);

31

32 ;

33 ⊡

process(clk)

34 :

begin

35 ⊝

if rising edge(clk) then

36

count <= count + 1;

37 🖒

end if;

38 🖨

end process;

39 :

40

41

leds(7 downto 0) <= std logic vector(count(27 downto 20));</pre>

42

43

44 ⊝ end rtl;

45

```

**←** This is a comment

```

--- simple "hello world" example

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

library unisim;

use unisim. VComponents.all;

8

9

10

11 🖯

entity top is port(

12

sysclk p : in std logic;

13

sysclk n : in std logic;

14

: out std logic vector(7 downto 0)

15

);

16 🖨

end top;

17

18 🖯

architecture rtl of top is

19

20

signal clk : std logic;

21

signal count : unsigned(27 downto 0) := (others => '0');

22

23

begin

24

25 ⊝

ibuf: IBUFDS

26

port map(

27

i => sysclk p,

28

ib => sysclk n,

29

o => clk

30 (

);

31

32 ;

33 ⊡

process(clk)

34

begin

35 🖯

if rising edge(clk) then

36

count <= count + 1;

37 🖨

end if:

38 🖯

end process;

39

40

41

leds(7 downto 0) <= std logic vector(count(27 downto 20));</pre>

42

43

44 end rtl;

45

```

Load packages from libraries

IEEE.std\_logic\_1164 has types for logic signals

★ IEEE.numeric\_std has numeric data types

unisim. VComponents has declarations and simulation data for device-specific primitives

```

--- simple "hello world" example

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

library unisim;

8

use unisim. VComponents.all;

9

10

11 🖯

entity top is port(

12

sysclk_p : in std_logic;

13

sysclk n : in std logic;

14

: out std logic vector(7 downto 0)

15

16

end top;

17

18 ⊖

architecture rtl of top is

19

20

signal clk : std logic;

21

signal count : unsigned(27 downto 0) := (others => '0');

22

23

begin

24

25 🖯

ibuf: IBUFDS

26

port map(

27

i => sysclk p,

28

ib => sysclk n,

29

o => clk

30 (

);

31

32 ;

33 ⊡

process(clk)

34 :

begin

35 🖯

if rising edge(clk) then

36

count <= count + 1;

37 🖨

end if;

38 🖯

end process;

39

40

41

leds(7 downto 0) <= std logic vector(count(27 downto 20));</pre>

42

43

44 end rtl;

```

Declare a VHDL block with ports

We give this block a name (top)

and define connections (ports) to the outside

top level ports correspond to actual FPGA I/O pins

```

--- simple "hello world" example

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

6

7

library unisim;

use unisim. VComponents.all;

8

9

10

11 🖯

entity top is port(

sysclk p : in std logic;

12

sysclk n : in std logic;

13

: out std logic vector(7 downto 0)

14

15

);

16 🖨

end top;

17

18 ☐ architecture rtl of top is

19

20

signal clk : std logic;

21

signal count : unsigned(27 downto 0) := (others => '0');

22

23

begin

24

25 🖯

ibuf: IBUFDS

26

port map(

27

i => sysclk p,

28

ib => sysclk n,

29

o => clk

30 🖨

);

31

32 ;

33 ⊡

process(clk)

34 :

begin

35 ⊝

if rising edge(clk) then

36

count <= count + 1;

37 🖒

end if;

38 🖨

end process;

39 :

40

41

leds(7 downto 0) <= std logic vector(count(27 downto 20));</pre>

42

43

44 end rtl;

45

```

Describe the VHDL block

```

--- simple "hello world" example

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

library unisim;

8

use unisim. VComponents.all;

9

10

11 🖯

entity top is port(

12

sysclk_p : in std_logic;

13

sysclk n : in std logic;

14

: out std logic vector(7 downto 0)

15

);

16

end top;

17

18 ─ architecture rtl of top is

19

20

signal clk : std logic;

21

signal count : unsigned(27 downto 0) := (others => '0');

22

23

begin

24

25 🖯

ibuf: IBUFDS

26

port map(

27

i => sysclk p,

28

ib => sysclk n,

29

o => clk

30 (

);

31

32

33 ⊡

process(clk)

34 :

begin

35 🖯

if rising edge(clk) then

36

count <= count + 1;

37 🖨

end if;

38 🖯

end process;

39 !

40

41

leds(7 downto 0) <= std logic vector(count(27 downto 20));</pre>

42

43

44 end rtl;

45

```

Declare internal signals we need

💢 consider signals more like wires, not as variables

can assign an initial state, though

```

--- simple "hello world" example

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

6

7

library unisim;

8

use unisim. VComponents.all;

9

10

11 🖯

entity top is port(

12

sysclk_p : in std_logic;

13

sysclk n : in std logic;

14

: out std logic vector(7 downto 0)

15

);

16 🖨

end top;

17

18 🖯

architecture rtl of top is

19

20

signal clk : std logic;

21

signal count : unsigned(27 downto 0) := (others => '0');

22

23

begin

24

25 🖯

ibuf: IBUFDS

26

port map(

27

i => sysclk p,

28

ib => sysclk n,

29

o => clk

30 (

);

31

32

process(clk)

33 ⊡

34

begin

35 🖯

if rising edge(clk) then

36

count <= count + 1;

37 🖨

end if:

38 🖯

end process;

39

40

41

leds(7 downto 0) <= std logic vector(count(27 downto 20));</pre>

42

43

44 🖨

end rtl;

45

```

Instantiate a different block

this one is from a library

it converts differential clocks to single-ended

we name this instance ibuf

we connect it to our signals

```

--- simple "hello world" example

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

library unisim;

8

use unisim. VComponents.all;

9

10

11 🖯

entity top is port(

12

sysclk_p : in std_logic;

13

sysclk n : in std logic;

14

: out std logic vector(7 downto 0)

15

);

16 🔿

end top;

17

18 ─ architecture rtl of top is

19

20

signal clk : std logic;

21

signal count : unsigned(27 downto 0) := (others => '0');

22

23

begin

24

25 🖯

ibuf: IBUFDS

26

port map(

27

i => sysclk p,

28

ib => sysclk n,

29

o => clk

30 🖨

);

31

32

33 ⊡

process(clk)

34 :

begin

35 🖯

if rising edge(clk) then

36

count <= count + 1;

37 🖨

end if;

38 🖨

end process;

39 !

40

41

leds(7 downto 0) <= std logic vector(count(27 downto 20));</pre>

42

43

44 end rtl;

45

```

#### a process

runs when specific events occur there: rising edge of clk allocate incremented value to count

(almost like software, isn't it?)

```

--- simple "hello world" example

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

library unisim;

8

use unisim. VComponents.all;

9

10

11 🖯

entity top is port(

12

sysclk_p : in std_logic;

13

sysclk n : in std logic;

14

: out std logic vector(7 downto 0)

15

16

end top;

17

18 ─ architecture rtl of top is

19

20

signal clk : std logic;

21

signal count : unsigned(27 downto 0) := (others => '0');

22

23

begin

24

25 🖯

ibuf: IBUFDS

26

port map(

27

i => sysclk p,

28

ib => sysclk n,

29

o => clk

30 (

);

31

32 ;

33 ⊡

process(clk)

34

begin

35 🖯

if rising edge(clk) then

36

count <= count + 1;

37 🖨

end if;

38 🖯

end process;

39

40

41

leds(7 downto 0) <= std logic vector(count(27 downto 20));</pre>

42

43

44 end rtl;

45

```

### connecting counter bits with LED

this is NOT a one time assignment

it connects signals like wires

every change in count will change the state of leds

```

--- simple "hello world" example

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

7

library unisim;

8

use unisim. VComponents.all;

9

10

11 @ entity top is port(

12

sysclk p : in std logic;

13

sysclk n : in std logic;

14

: out std logic vector(7 downto 0)

15

);

16 end top;

17

18 ─ architecture rtl of top is

19

20

signal clk : std logic;

21

signal count : unsigned(27 downto 0) := (others => '0');

22

23

begin

24

25 🖯

ibuf: IBUFDS

26 :

port map(

27

i => sysclk p,

28

ib => sysclk n,

29

o => clk

30 (

):

31

32 ;

33 ⊡

process(clk)

34 :

begin

35 🖯

if rising edge(clk) then

36

count <= count + 1;

37 🖨

end if:

38 🖯

end process;

39 :

40

41

leds(7 downto 0) <= std logic vector(count(27 downto 20));</pre>

42

43

44 end rtl;

45

```

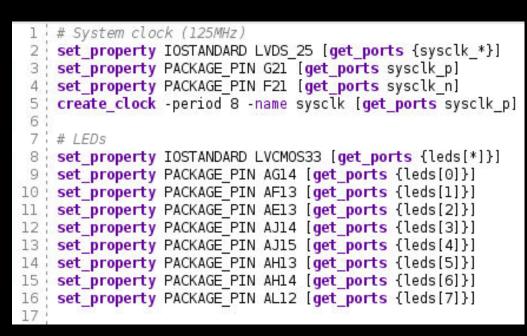

#### one missing ingredient:

our design software needs to be told what pins clock and LEDs are connected to and what logic standard to use define constraints (separate file)

(this information from zcu102 documentation)

### firmware workflow

There is a number of steps between VHDL and a blinking LED:

#### synthesis

translate VHDL into netlist (optimised components with connections)

#### implementation

map design onto actual FPGA resources, assign place to entities and route signals along the fabric

#### bitfile generation

create actual bitstream that can be uploaded to device

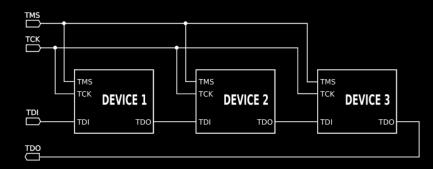

#### **JTAG** configuration

connect to device via serial JTAG interface and configure it! most high-end FPGAs use volatile RAM to store configuration

→ need to reconfigure with JTAG after each power-up or store firmware in external flash ROM

JTAG interface can have several devices in series

- \* e.g. multiple FPGAs

- or a FPGA and a flash ROM for non-volatile firmware storage All devices identify themselves, so software can verify expected type

Some boards have built-in JTAG controllers, just need USB cable. Others need external USB programmers:

JTAG connection can be used for debugging! Logic analyser cores

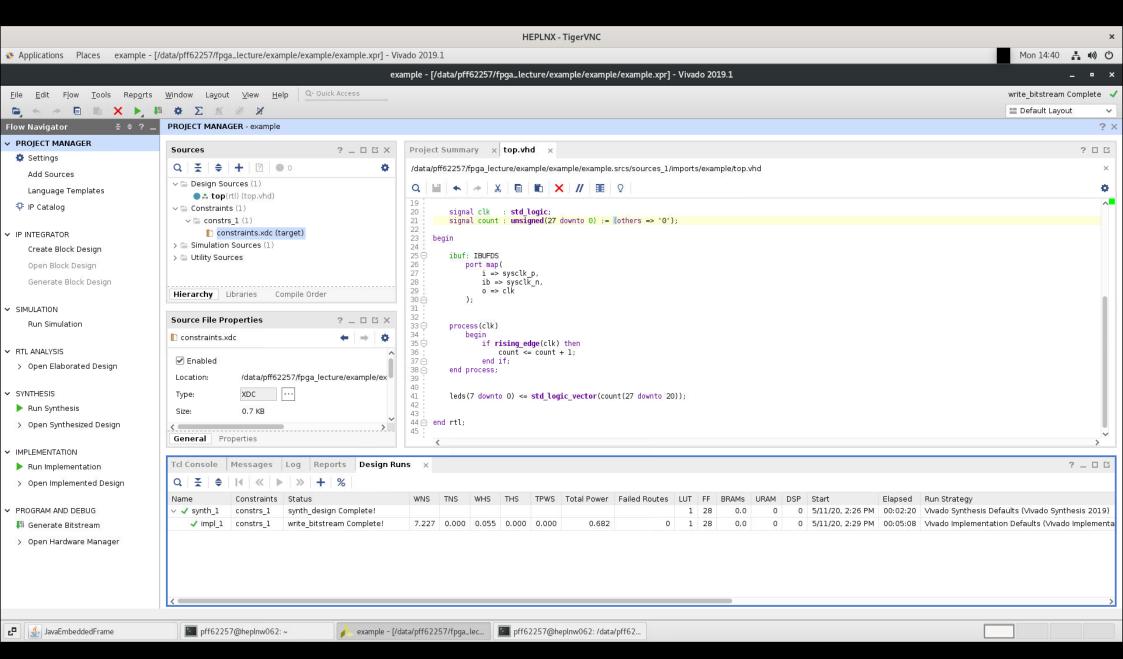

### Xilinx Vivado

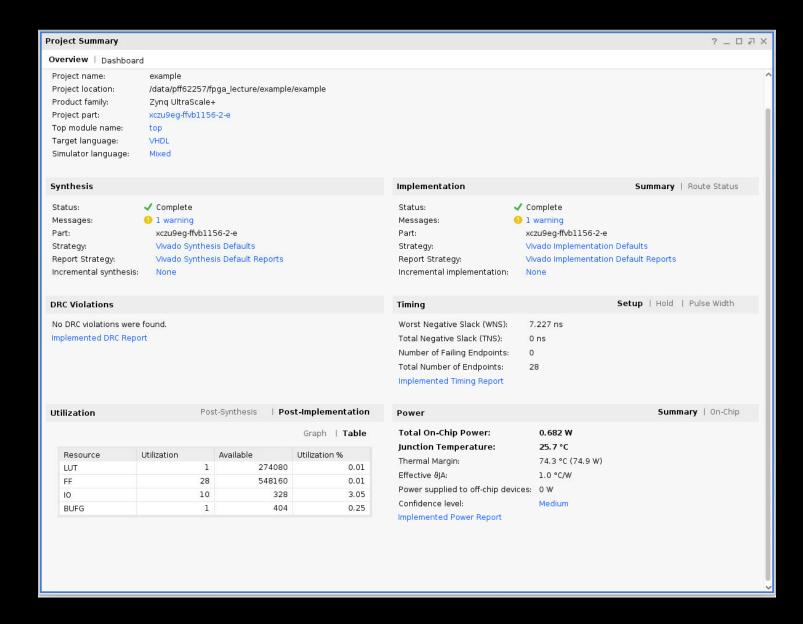

### Vivado report

#### Report after building our example firmware for the zcu102:

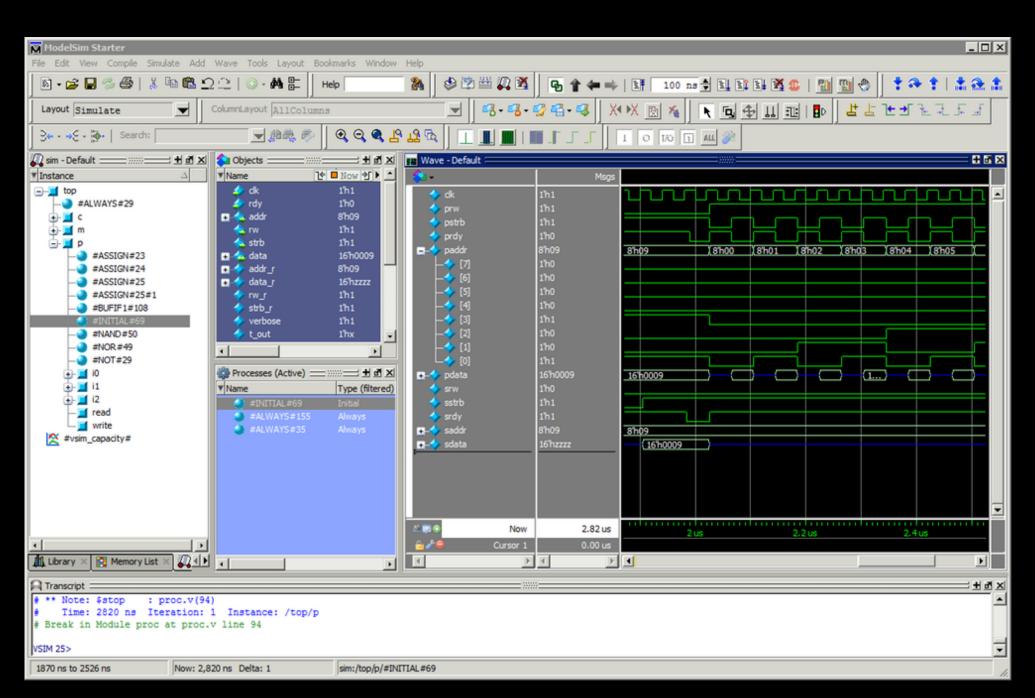

### simulation

More complex firmware is best tested in simulation first A very powerful tool for verification and debugging!

- \* exactly reproducible inputs

- much faster turnaround time than tests on hardware

- but not always a fully accurate reflection of timing, especially when timing is marginal or outside specifications

- comparison of firmware output on simulation and on actual hardware is often part of verification procedure

Vivado has an integrated simulator Third party software exists (e.g. Siemens/Mentor Graphics QuestaSim)

### simulation

# last topic: how to approach a BIG firmware project

software development: distributed, collaborative, version controlled,

unit tests, release management

firmware development: lonesome engineer with hard disk full of zip files

# last topic: how to approach a BIG firmware project

software development: distributed, collaborative, version controlled,

unit tests, release management

firmware development: lonesome engineer with hard disk full of zip files

## large firmware projects

#### Firmware projects like CMS L1 trigger are very demanding:

- \* very complex

- need to be very reliable

- x subject to international collaboration and peer review

#### Need to work much more like with large software projects:

- modularity (leave the hardcore stuff to top experts)

- \* version control and release management

- rigorous testing, project supervision

#### CMS L1 trigger firmware project:

- \* separate framework and algorithm firmware

- \* script-based firmware build system (also enforces module structure)

- git repository (with automatic nightly builds)

- formal developer and user support (ticket system)

- very successful model, proven in LHC run 2 already

### conclusion

27.00-00

### **Key points:**

FPGA programming by firmware has many similarities with software development, but important differences

## | とt 8 t 3 | | コ

We are moving more and more functionality into FPGAs, e.g. in L1 trigger.

We have a lot more people who know how to write software than how to write firmware. This has to change.

I hope I demonstrated today that writing firmware is no voodoo.